总线和输入输出系统

概述

总线是一组能为多个部件分时共享的公共信息传输线路

分时: 指同一时刻只允许有一个部件向总线发送信息,如果系统中有多个部件,则它们只能分时的向总线发送信息

共享: 指总线上可以接多个部件,各个部件之间互相交换信息都可以通过这组线路分时共享

早期计算机外部设备少时多采用分散连接方式,不易实现随时增减外部设备。为了更好的解决 I/O 设备和主机之间连接的灵活性问题,计算机的结构从分散连接发展为总线连接

总线通常分为地址总线、数据总线、控制总线,总线上有主设备和从属设备。

分类

层次连接:

- 片内总线:芯片内部的总线,它是 芯片内部寄存器与寄存器之间,寄存器与 之间的公共连接线。

- 系统总线:计算机系统内各功能部件 (、主存、 接口) 之间相互连接的总线。按系统总线传输信息内容不同,又可分为三类: 数据总线,地址总线和控制总线;

- 通信总线:用于计算机系统之间或计算机系统与其他系统 (如远程通信设备,测试设备) 之间信息传送的总线,通信总线也称为外部总线。

数据位数:

- 并行总线:逻辑时序比较简单,电路实现起来比较容易,但是信号线数量多,占用更多的布线空间;远距离传输成本高昂;由于工作频率较高时,并行的信号线之间会产生严重干扰,对每条线等长的要求也越高,所以无法持续提升工�作频率;

- 串行总线:只需要一条传输线,成本低廉,广泛应用于长距离传输;应用于计算机内部时,可以节省布线,但是在数据发送和接收的时候,要进行拆卸和装配,要考虑串行和并行转换的问题。

现在大部分都是使用串行的,如 和 协议等,因为其可以用频率弥补。

用法:专用总线、公用总线。

总线结构

单总线结构

,主存, 设备 (通过 接口) 都连接在 一组 总线,允许 设备之间, 设备和 之间或 设备与主存之间直接交换信息。

优点: 结构简单,成本低,易于接入新的设备

单总线并不是指只有一根信号线,系统总线按传送信息的不同可以细分为地址总线,数据总线和控制总线

双总线结构

有两条总线,一条是主存总线,用于 ,主存和通道之间进行传送,另一条是 总线,用于多个外部设备与通道之间进行数据传送。

优点:将较低速的 设备从单总线上分离出来。实现存储器总线和 总线分离

缺点:需要增加硬件等通道设备

支持突发 (猝发) 传送,送出一个地址,收到多个地址连续的数据

通道是具有特殊功能的处理器,能对 设备进行统一管理。通道程序存放在主存中

三总线结构

在计算机系统各部件之间采用 条各自独立的总线来构成信息的通路。这三条总线分别为主存总线, 总线和直接内存访问 总线 ( 直接内存访问)

优点:提高了 设备的性能,使其更快的相应命令,提高系统的吞吐量

缺点:系统工作效率较低

通信方式

同步通信方式

与时钟同步,速度快,接口逻辑简单,但是所有的设备需要是一致的,且时钟速率依慢速设备而定;当总线太长时会有时钟偏移的问题。

异步通信方式

无时钟信号,使用握手协议,通常分为非互锁、半互锁和全互锁方式;也有串行异步通信,无需时钟信号也无需握手协议

全互锁的流程如下:

- 先使数据信号保持有效;

- 在发送一个表示数据准备好的信号,接收设备开始接收数据;

- 接受完毕后返回一个应答信号,表示接受完毕。

串行异步通信需要设定好发送方和接受方的数据传输速率,有没有校验位等,当接收方检测到一个起始位之后,就会每隔一定的时间采样数据,直到采样到停止位(1/1.5/2 位),数据位一般不会太长(5,7,8 位等)。

总线仲裁

菊花链

使用总线的优先级由 总线可用 线所连接部件的物理位置来决定,离总线控制器越近的部件其优先级越高;叫菊花链的原因是因为 总线可用(Bus Grant) 的线直接接入第一个部件,再由第一个部件引出接入第二个,一次类推,像花环一样串起来,并依次实现优先级。

此外,还有两条线为 (都是默认高电平),所有部件都接入这两个线;当一个部件需要使用总线时,其将 线置为低电平,总线仲裁其会将 线置为低电平,传给第一个需要使用总线的部件,而其他部件只能等待。

使用总线的部件会将 线置为低电平表示有部件使用总线,总线仲裁时也只会在总线非忙��时进行。

计数器定时查询(轮询)

将上述的 使用 条线代替,满足 , 为部件的个数,当总线空闲时进行轮询,部件中也有 个线与之相连,可以以此判断总线仲裁器询问的是哪个部件。

独立请求

每个部件单独将 和 接入总线仲裁器,共用一个 线,分配速度高,且优先级可以由总线确定。

分布式仲裁

分布式仲裁不需要仲裁器,但是仍然需要有 BR 和 BB,以此进行相互监听,防止冲突。

自举式分布式仲裁: 硬布线, 个部件就有 个 ,优先级低的部件要同时监听所有优先级高的 线。

链式分布式仲裁:形式与菊花链的仲裁方式相似,但是没有仲裁器,而是使用一个令牌从第一个部件向后传递,令牌会定时生成。

典型总线

内总线(系统总线)有 、、 总线;外总线(通信总线)有 、、、、、 等。

总线和 总线有很大的区别, 总线使用差分的形式进行串行传输,输入输出都是两根,并且支持全双工通信,属于端到端的传输形式;而 总线类似一种树形的总线;但是其软件是兼容的,因此叫 .

USB 总线

,通用串行总线,由七家公司联合开发,其总线信号有 (电源),(接地),(信号正),(信号负);有三种传输速率,高速、全速、低速。

加入了超速传输模式,速率可达 ,类似于 ,使用两跟数据线差分传输数据,同时为了防止高速串行传输数据造成丢失,需要使用特殊的编码方式,将传输数据均衡化,不会出现太多连续的 和 , 中也使用了该方法。

I/O 接口作用及模型

接口是两个系统或者两个部件之间的交接部分,可以是两种硬件设备之间的连接电路,也可以是两个软件之间的共同逻辑边界。

那么 接口通常是指 设备和主机之间的一个硬件电路及其相应的软件控制,其内部有数据寄存器(缓冲器)、状态寄存器、控制寄存器、命令寄存器、 控制逻辑电路等,一边与总线相连接,一边与 设备连接。

接口的功能有:

- 选址功能

- 传送命令

- 传送数据

- 信号形式匹配

- 负载匹配

- 错误检测

- 设备选择、控制

- 数据缓存、速度匹配

- 支持中断。 . .

I/O 地址的编码方式

存储器映射方式(统一编址)

将主存与 设备放在同一个地址空间中,使用与主存相同的指令和控制信号,不需要专门的 指令可以简化控制,在地址空间确定的情况下,两者的地址扩充相互制约。

I/O 映射方式(独立编址)

使用独立的地址空间,要求系统提供专门的 指令,并且采用与主存不同的读/写控制信号,便于系统调试与维护,便于主存与 地址空间的扩展,但是 设备的操作不够灵活。

输入输出技术

一般有四种:

- 程序查询方式

- 中断方式

- 直接存储器存取 () 方式

- 通道方式

程序查询方式

不断地轮询 设备,硬件简单,但是 占用高;常用于简单的设备,如单片机等。

中断方式

接口电路和 都需要添加中断的相应的电路,当外设向 发射了中断请求,如果现在 运行的程序没有屏蔽中断,��则会进行中断处理,包括保护断点(保存 和 ),保护现场(保存通用寄存器),执行中断服务,恢复现场,中断返回等。

中断可以来自 内部和外部,内中断也被称为异常,常见的有溢出中断、缺页中断。

中断源的选择也是需要仲裁优先级的,一般使用菊花链(无优先仲裁电路)或者分组独立请求的方案。

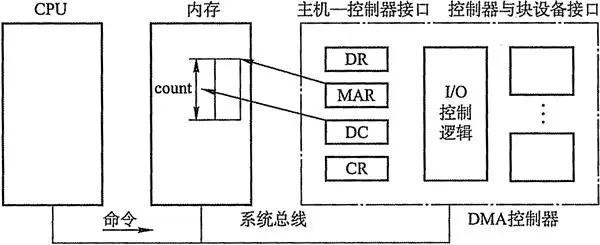

DMA 方式

中断方式中数据交换必须经过 中的寄存器,因此速度受限, 直接存储器存取的基本思想是在 设备直接直接建立数据交换通路,彻底解放 ,特点如下:

- 基本单位是数据块;

- 从设备直接送入内存,反之亦然;

- 仅在传送一个或多个数据块的开始和结束时,才需要 干预,整块数据的传送是在 控制器下完成的。

DMA 控制器中有如下 4 类寄存器:

- 命令/状态寄存器(CR),接受 的 命令、有关控制信息或设备状态;

- 内存地址寄存器(MAR),输入时,其存放传输数据到内存中的启始目标地址,输出则存放数据在内存中的源地址;

- 数据寄存器(DR);

- 数据计数器,存放本次要传送的字(节)数;

通道控制方式

通道是指专门负责输入/输出的处理机, 通道方式是 方式的发展,可以进一步减少 的干预,传输单位由块变为组,同时可以实现 、通道、 设备三者的并行操作。

读写时, 向通道发送一条 指令,给出要执行的 通道程序 的首地址和要访问的 设备,通道会执行通道程序;结束时会向 发送中断请求。

指令类型单一,没有自己的内存,通道程序放在主机的内存当中。

DMA 需要 CPU 控制传送数据块大小和内存位置,而通道则是由通道程序控制;一个 DMA 控制器只能对应一个设备,而一个通道可以对应多台设备。